StudentShare

Our website is a unique platform where students can share their papers in a matter of giving an example of the work to be done. If you find papers

matching your topic, you may use them only as an example of work. This is 100% legal. You may not submit downloaded papers as your own, that is cheating. Also you

should remember, that this work was alredy submitted once by a student who originally wrote it.

Login

Create an Account

The service is 100% legal

- Home

- Free Samples

- Premium Essays

- Editing Services

- Extra Tools

- Essay Writing Help

- About Us

✕

- Studentshare

- Subjects

- Information Technology

- Architecture and Functionality of the Cisco 1006 Series Router

Free

Architecture and Functionality of the Cisco 1006 Series Router - Lab Report Example

Summary

The paper "Architecture and Functionality of the Cisco 1006 Series Router" deals with individual performance and functionality for each component of the router is demonstrated along with a comparison and a benefits table for elaborating the topic and to link it with its real benefits. …

Download full paper File format: .doc, available for editing

GRAB THE BEST PAPER92.2% of users find it useful

- Subject: Information Technology

- Type: Lab Report

- Level: Undergraduate

- Pages: 4 (1000 words)

- Downloads: 0

- Author: major82

Extract of sample "Architecture and Functionality of the Cisco 1006 Series Router"

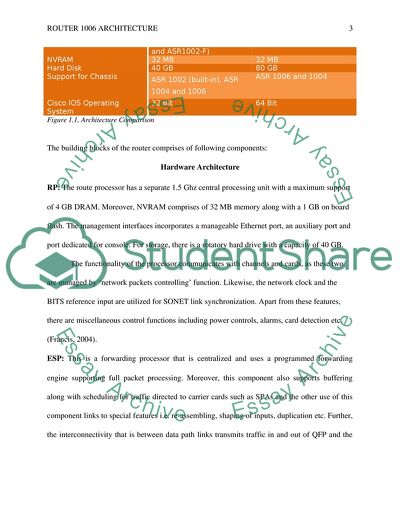

Full Paper Full Paper Architecture and Functionality Physical Architecture The physical architecture of the router comprises of SPA interface processor that can take up to 4 HH SPAs. Likewise, the SPA slots can be used for utilizing existing SPAs. Moreover, there is an embedded services processor that has 40 cores along with traffic manager. Further, there is a route processor that can support up to 16 GB DRAM with the speed of 2.66x2 GHz. In addition, there are other chassis options as well incorporating SPAs, SIP, ESP and RP. The route processor of the router has maximum speed of 1.5 GHz with a support of adding six routes (Newman, 2009). Likewise, this component also contains a hot swappable hard disk drive enclosure with a second generation route processor having speeds up to 2.66 GHz dual core Xeon processor. Moreover, the hardware architecture of the router has a built in forwarding quantum flow processor with the speed of 800MHz and operates on 10 Gbps (Joseph & Chapman, 2009). The SPA interface processor is constructed on first generation architecture with a 10Gbps aggregated performance with the speed of 800MHz. Figure 1.1 illustrates the differences between two models on different architectures below (Joseph & Chapman, 2009):

ASR 1006 RP1

ASR 1006 RP2

CPU

Freescale 1.5GHz

Dual-Core Intel Xeon Processor 2.67GHz

Memory

Memory 2GB default 2x1GB)

4GB maximum (2x2GB)

RP1 with 4GB built in

ASR1002 and

ASR1002-F

8GB default (4x2GB) 16GB

maximum (4x4GB)

e-USB bootflash

Built-in eUSB bootflash 1GB (8GB on ASR-1002 and ASR1002-F)

2GB

NVRAM

32 MB

32 MB

Hard Disk

40 GB

80 GB

Support for Chassis

ASR 1002 (built-in), ASR

1004 and 1006

ASR 1006 and 1004

Cisco IOS Operating System

32 Bit

64 Bit

Figure 1.1, Architecture Comparison

The building blocks of the router comprises of following components:

Hardware Architecture

RP: The route processor has a separate 1.5 Ghz central processing unit with a maximum support of 4 GB DRAM. Moreover, NVRAM comprises of 32 MB memory along with a 1 GB on board flash. The management interfaces incorporates a manageable Ethernet port, an auxiliary port and port dedicated for console. For storage, there is a rotatory hard drive with a capacity of 40 GB.

The functionality of the processor communicates with channels and cards, as these two are managed by ‘network packets controlling’ function. Likewise, the network clock and the BITS reference input are utilized for SONET link synchronization. Apart from these features, there are miscellaneous control functions including power controls, alarms, card detection etc. (Francis, 2004).

ESP: This is a forwarding processor that is centralized and uses a programmed forwarding engine supporting full packet processing. Moreover, this component also supports buffering along with scheduling for traffic directed to carrier cards such as SPAs and the other use of this component links to special features i.e. re-assembling, shaping of inputs, duplication etc. Further, the interconnectivity that is between data path links transmits traffic in and out of QFP and the scheduler that work for allocating QFP between ESI’s. In addition, this component also supports cryptography, mid plane links etc.

SPA / SIP: The SPA interface processor is capable of supporting 4 SPAs, however, there is a limitation, as it does not participates in forwarding. Likewise, this component supports limited quality of service, as the mechanism can identify low and high packet classification. Moreover, there is also a support of 128 MB oversubscribed buffering (Lucas, 2009). For getting detailed information for the dropped packets, this component provides statistics on the packets that are dropped. Likewise, the mid-plane links are managed by SIP central processing unit

Behavior & Performance

Fig 1.2 links the functionality of the router with the IOS and hardware resources along with the benefits that can be achieved.

Features of IOS

Hardware Resource

Paybacks

Access Control List (ACL)

Range lookup for ACL and TCAM

The lookup is robust with no service degradation

uRPF

Unit for pointer look up

uRPF is enabled that facilitates minor service degradation

NAT Session Lookup

Hash mode is set to read

In spite of having large number of sessions, performance is not affected

Policing

PPE and QFP

DDOS prevention by enabling CoPP with no service impact

IPSec

Crypto Engine

A built in high tech multi core chip that handles the service impact and assures minor latency

Figure 1.2

These two components are essential for delivering acceptable service levels to the business. Likewise, the redundant network not only maintains the service quality in normal situations but in critical situations as well. For instance, a link has failed to respond and it needs to be rerouted from the faulty route to an operational and active route. Supporting this feature requires an aggregation service supported router with next generation processing capabilities. Likewise, Cisco has established a Quantum Flow Processor that is the first combined chip that can be re-programmed. Moreover, the processor supports a large scale parallel processing with quality of service, next level memory management and re programmable integrated services. With all these features, this router commands in service implementation and scalability leading to a minimized implementation time with low cost of ownership. The Wide Area Services edge facilitates robust and high data rates on the ASR 1006 series. In addition, the ASR 1006 provides optimization in terms of redundancy allocation for routers that maintain high availability. Figure 1.3 demonstrates the number of active routers against the number of standby routers.

Fig 1.3 Sources: (Buggey, 2007)

Following are the factors that are directly proportional to accomplish and assist business objectives (Chen, H., Li, F. H., & Xiao, 2011):

Considerable raise in WAN bandwidth and volume, when compared to previous router series.

Enhanced security features by activating Cisco Webex node on the router along with Unified border element and high definition multimedia content, Public switched telephone networks (PSTN), application performance optimization etc.

A redundant link available for maintaining connectivity over the WAN in case of primary link failure

Alternate power sources ensure operational continuity and contingency planning on its own.

Robust hardware architecture bundled with data split-up and control for system availability

Contingency is also available for route processing and route forwarders in case of failover initiation

Redundancy for Cisco IOS that can be operated on a non-redundant hardware

Remote access for router to restart or remove any fault that may arise via In services software upgrade

A high tech security mechanism is available for countering attacks and act as a preventive control along with ensuring compliance

Security mechanism activation do not affect the performance of route processing and other associated services

The simple holistic configuration approach saves cost, time and resources for the organization

The privately established remote sites are secured by aggregation mechanism built in the router

Encrypted Internet access, firewall and virtual private network services are also considered as an enhanced security feature

Conclusion

The report has primarily discussed about the physical and hardware architecture of the Cisco 1006 series router. Likewise, individual performance and functionality for each component of the router is demonstrated along with a comparison and a benefits table for elaborating the topic and to link it with its real benefits i.e. business objectives. Lastly, the fact was established and was associated with the features, functions and services with a realistic scenario of assuming and linking them with the organization’s objective i.e. availability of service, quality of service, security and redundancy.

References

Chen, H., Li, F. H., & Xiao, Y. (2011). Handbook of Security and Networks. Hackensack, NJ: World Scientific.

Francis, B. (2004). Cisco Routers Add Services. Infoworld, 26(37), 19.

Joseph, V., & Chapman, B. (2009). Deploying QoS for cisco IP and next generation networks: The definitive guide Elsevier Science

Lucas, M. (2009). Cisco routers for the desperate [electronic resource] : router and switch management, the easy way / Michael W. Lucas. San Francisco : No Starch Press, c2009.

Newman, D. (2009). Ciscos ASR router: A strong first effort. (cover story). Network World, 26(2), 1.

Images:

Buggey,T ( 2007) Storyboard for Ivans morning routine. Diagram. Journal of Positive Behavior Interventions, 9(3), 151.

Glossary

SPA: Shared Port Adapter

BITS: Building Integrated Timely Supply

QFP: Quantum Flow Processor

ESI: Enhanced SerDes Interface

Read

More

sponsored ads

Save Your Time for More Important Things

Let us write or edit the lab report on your topic

"Architecture and Functionality of the Cisco 1006 Series Router"

with a personal 20% discount.

GRAB THE BEST PAPER

✕

- TERMS & CONDITIONS

- PRIVACY POLICY

- COOKIES POLICY